Universal Interfaces

The new ATXMEGA controllers have a variety of hardware features and components.

The new ATXMEGA controllers have a variety of hardware features and components.

In contrast to the „older“ Attiny and Atmega controllers, the configuration structure („Defines“) from Atmel was fundamentally revised. With ATxmega all registers are consistently and cleanly separated by appropriate namespaces and they use all the same way for the naming of eg bit names, bit groups and configuration registers.

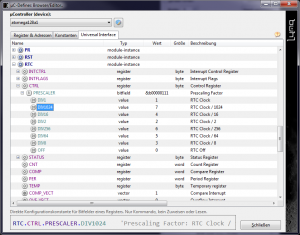

This lets you add these pre-assigned manufacturer „defines“ divided neatly into groups and this are correspondingly more manageable. In the Luna IDE „Defines (window)“ the index has also been a corresponding group expanded view (see picture).

In the Defines-Browser/Editor (IDE)

In the Defines-Browser/Editor is for Atxmega-devices a hirarchical overview available. This overview contains all available hardware-modules, registers, bitfields and configuration constants for the selected device.

A click on an element shows automatically a syntax example on the bottom for the usage in Luna-Source. A double-click on an element insert this to the source code at the current cursor position, including a short description as comment.

Source Level

The universal interface provides a simplified way for the direct configuration of the ATXMEGA Components. This means that all group names represent a hardware component that can be addressed in the source code using the usual dot notation.

Basically, this differs only slightly from the configuration via the Avr class using Avr.<Registername>.<Registerbit>, with the only difference that:

- less typing is necessary

- Accesses to bits and bit groups automatically dependent to the current component,

- Accesses to registers automatically with the correct data type and

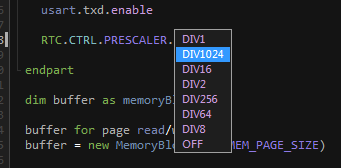

- in the IDE presorted the AutoComplete for the register used.

Same name Luna interfaces

Same name Luna interfaces, such as USARTC0 are combined. That both variants using to the same time are possible. The available functions are Luna interface extensions that can be applied to this component (eg „usartc0.ReadByte“ and others).

Application

The access to a component is determined by:

Component.Register[.Bit/Bit group] or

Component.Vector

Here, read and write accesses are possible. Extent that makes sense for each individual component, reveals the datasheet of the controller.

- Component is the name of the component to be addressed, for example, eg. RTC

- Register is the register of the component to be addressed, eg. CTRL. The leading indication of the component name, for example, „RTC_“ (see picture) is omitted. The compiler knows from the definition of how large is the data width of the register (see picture, „Size“ column). Reading or writing is done so automatically in the data width defined by the manufacturer.

- Bit/BitGroup (optional) is the bit or group of bits to be addressed in the register. The leading indication of the component name, for example, „RTC_“ (see picture) is omitted. You can access a single bit in boolean (0 or 1), a group of bits assigns the corresponding value depending on the number of bits in the group. The compiler reads or sets the value correctly in the register without attaching the surrounding bits. The available bits that can be addressed, ending with _BP, groups with the extension _GM in the Defines Overview. All names are adopted from the ATxmega data sheet 1:1.

- Vector is an interrupt vector of the component, which one of a name Interrupt-Serviceroutine can assign (only assignment possible).

Examples

The Access to the single bit SYNCBUSY in the register STATUS of the component RTC are:

bit = RTC.STATUS.SYNCBUSY //reading RTC.STATUS.SYNCBUSY = bit //writing (make no sense on this bit, only for example)

The access to the bit group PRESCALER (3 Bits) in the register CTRL of the component RTC are:

value = RTC.CTRL.PRESCALER //reading RTC.CTRL.PRESCALER = value //writing

The register can be configured directly without assignment. The AutoComplete provides all associated and possible configurations also here:

RTC.CTRL.PRESCALER.DIV1024 //configure prescaler bitfield 'same per assignment are: RTC.CTRL.PRESCALER = RTC_PRESCALER_DIV1024_gc

The access to the whole register PER (here: word) of the componente RTC are:

value = RTC.PER //reading RTC.PER = value //writing

Assign a service routine to the interrupt vector OVF_VECT of the component RTC:

RTC.OVF_VECT = name isr name .. endisr